### Evolving Peering with a New Router Architecture

Jean-David LEHMANN-CHARLEY Compass-EOS RIPE 67, Athens

jd.lehmann@Compass-EOS.com

# Peering Requirements / Challenges

- Availability

- Critical service on limited number of nodes

- HA hardware features

- Scalability

- Bandwidth (100G interconnects)

- Port density (Nx10G, 100G)

- BGP scaling

- FIB convergence

- Dual stack IPv4/IPv6

- MP-BGP to support both AFs

- RIB/FIB scaling

# Peering Requirements / Challenges

- Stable/evolved BGP implementation

- Flexible routing policy framework

- 4-byte ASN support, capability negotiation route reflectors, confederations

- Security

- Infrastructure filtering

- Accounting (Netflow v9, IPFIX)

- Control plane protection

- Colocation Cost control

- Space

- Power Consumption

## Lessons from the Data Center Market

#### **Monolithic Mainframes**

#### Virtualized Data Center

## Clustering & Virtualization Brought Efficiency to the Data Center

## **Evolution of Industries**

Data Centers

### Can Networks Follow The Data Center Evolution?

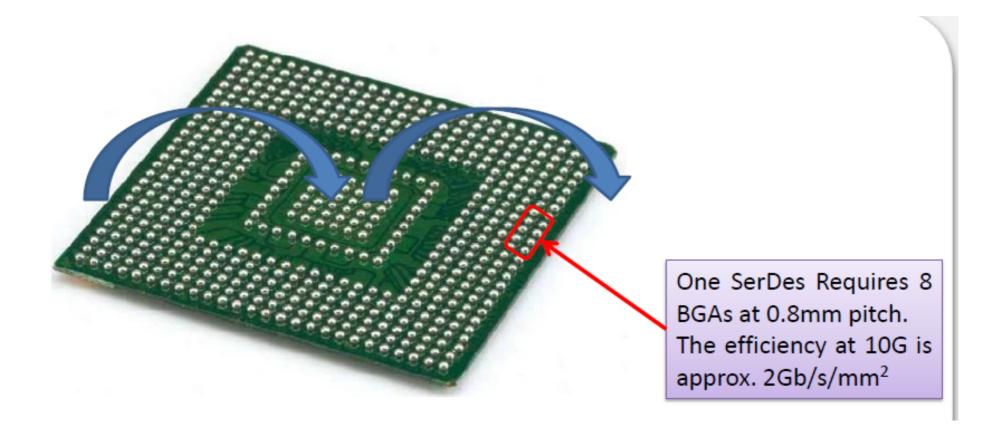

### So why do we have "Mainframe-like" routers?

### It's Electronics and Copper Limitations

## Zooming in on the challenge

- Chip I/O at speeds of 100G is limited to a few centimeters

- Requiring Amplification every 2/3 cm

- Requiring MORE electronics

- Requiring MORE cooling

- Requiring MORE space

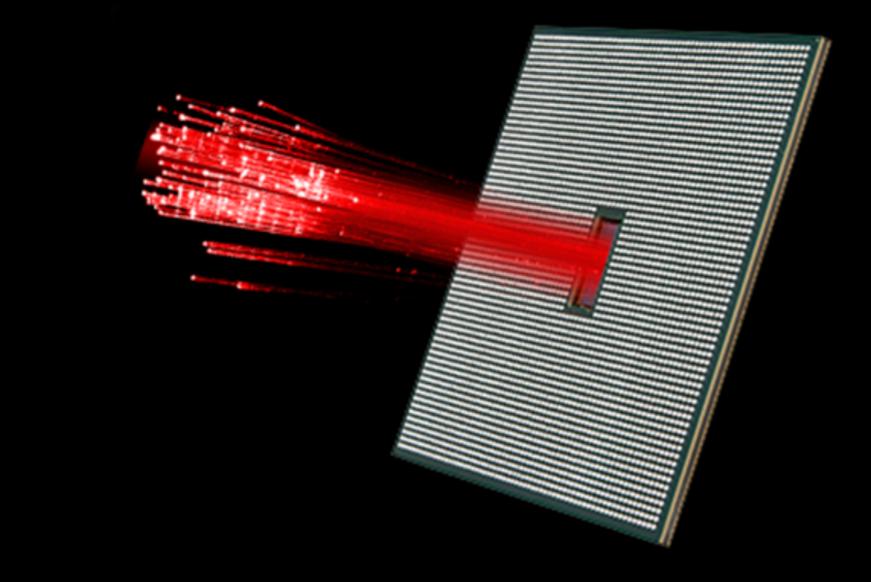

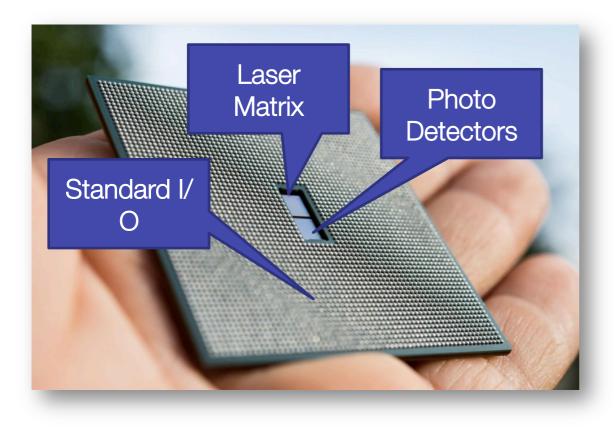

# Compass-EOS icPhotonics<sup>TM</sup>

### World First Chip-to-Chip Optical Interconnect

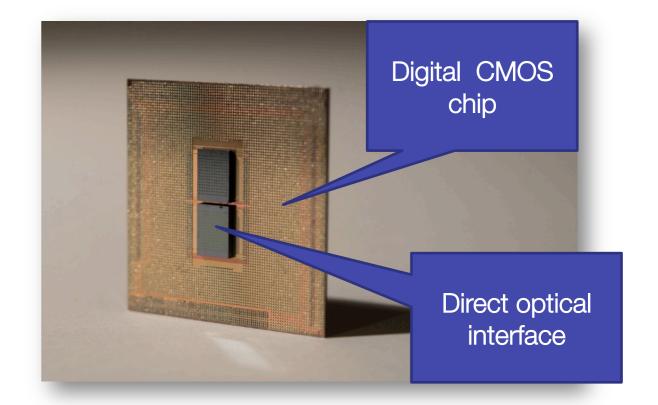

### *icPhotonics*™ World's First Chip-to-Chip Optical Interconnect

- 1.34Tb/s Full Duplex Bandwidth

- Order of magnitude higher Chip I/O Density. 64Gb/a per mm2

- Passive optical links that stretch to Hundreds of Meters vs.

Centimeters with Electronics

- Direct Coupling to CMOS Chip

- Low energy consumption: 10pJ/ bit

- Dozens of Patents Covering Technology & Processes

- Flexible form factor

- Deployed in Production

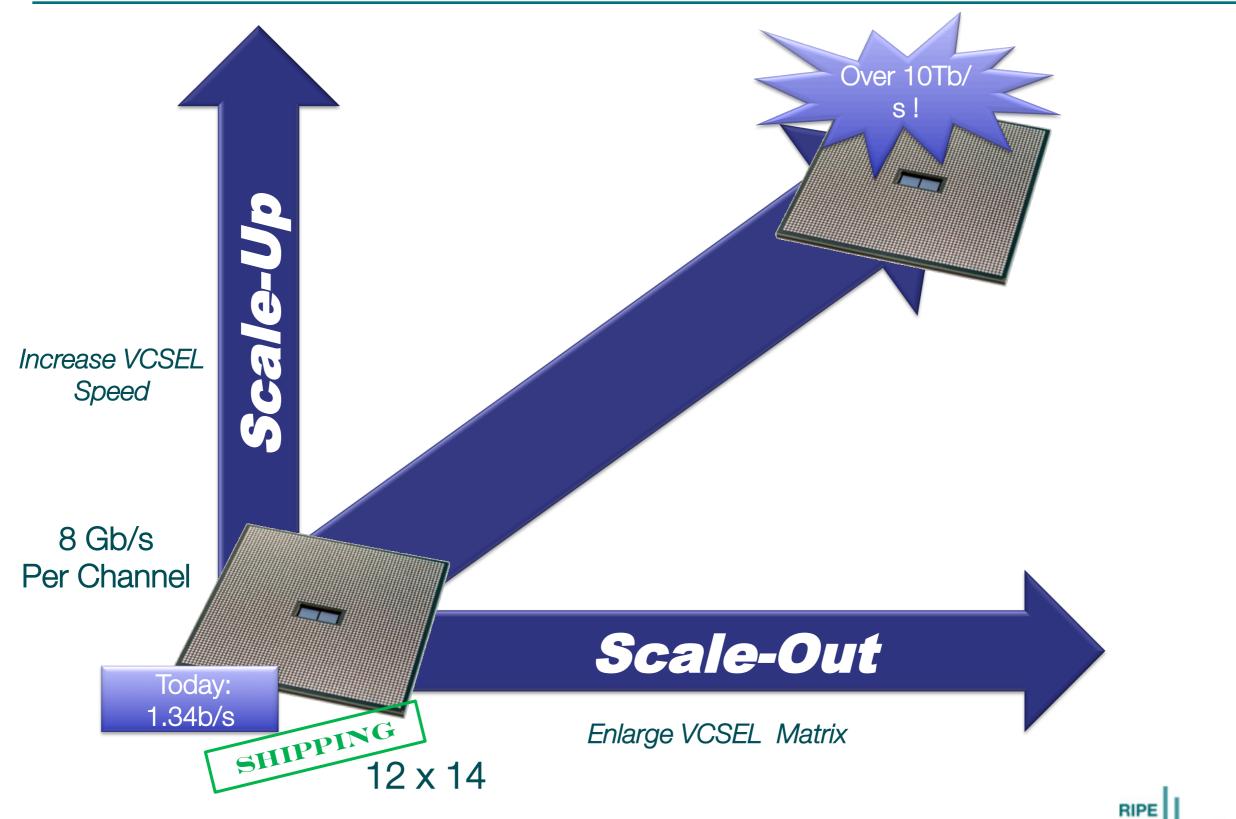

### Scaling icPhotonics<sup>™</sup> to Even Higher Capacities

*icPhotonics*<sup>™</sup> – *Inter-Chip Photonics*

## Revolutionizing Backplane Connectivity

The Traditional Way: Multi-Layer Midplane and Switching Fabric The Compass-EOS Way: icPhotonics™ Passive Optical Mesh

Complex High Costs High Power Larger Systems Limited BW/Slot Simple Lower Costs Lower Power Smaller Footprint Unlimited BW/Slot

RIPE

## Enabling a simplified routing building-block

Asaf SOMEKH, Oct 15th, 2013

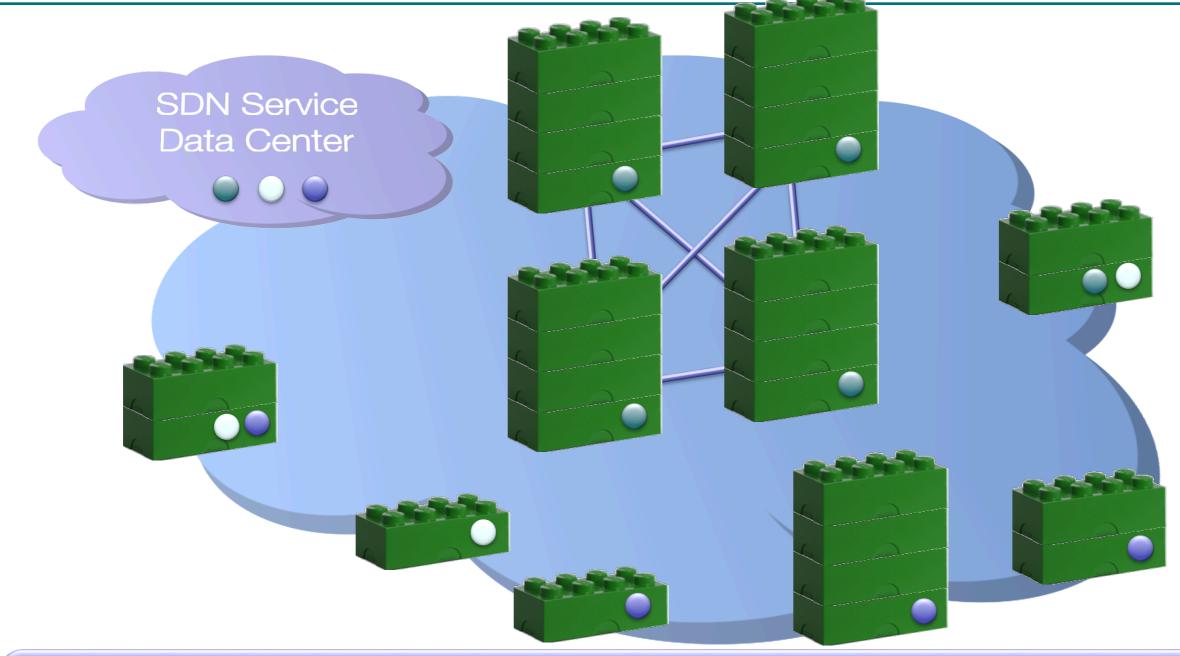

### Enabling the Vision of Network Virtualization

### Simplifying the Network with Routing Building Blocks & SDN

# How icPhotonics plays

| Requirement                      | Solution                                                                                         |

|----------------------------------|--------------------------------------------------------------------------------------------------|

| Colocation Cost Efficiency       | Optical backplane reduces the routers physical foot print and power consuptions                  |

| Efficient port density and scale | Congestion free optical mesh enables dense 100G solutions                                        |

| Availability                     | Higher MTBF with passive optical<br>backplane replaces active electronics<br>based fabric boards |

| Security                         | No "Security Vs. Capacity" Compromises –<br>Full mesh based centralized policing                 |

### Enabled by Compass-EOS icPhotonics<sup>TM</sup>

# Questions?

Asaf.Somekh@Compass-EOS.com

Asaf SOMEKH, Oct 15th, 2013